# Correlation of Timing Measurements

**Application Note 398-2**

| Introduction                                              | p. 2 |   |

|-----------------------------------------------------------|------|---|

| 1. Test system error terms                                | p. 3 |   |

| 2. Error terms due to interfacing                         | p. 4 |   |

| 2.1 AC loading of tester output<br>by DUT                 | p. 4 |   |

| 2.2 DUT input threshold versus actual tester drive levels | p. 5 |   |

| 2.3 DUT output AC loading by tester                       | p. 5 |   |

| 2.4 DC threshold                                          | p. 6 |   |

| considerations                                            | p. 7 |   |

| 2.5 DUT wiring                                            | Ρ    |   |

| 2.6 DUT specifics                                         | p. 7 |   |

| 3. Correlation procedure                                  | p. 8 |   |

| 3.1 Calibration                                           | p. 8 |   |

| 3.2 Eliminate system roundtrip error term                 | p. 9 |   |

| 3.3 Compensation for capacitive                           | p. 1 | 0 |

| load                                                      | p. 1 |   |

| 3.4 Input level considerations                            | p. 1 |   |

| 3.5 Device output DC loading                              | Γ.   | _ |

| 3.6 Comparator reference adjustment                       | p. 1 | 0 |

| 3.7 DUT specifics                                         | p. 1 | Λ |

| 3.7 DOT specifics                                         | p. 1 | U |

| 4. "Golden" device adjustment                             | p. 1 | 1 |

| 4.1 Threshold adjustment                                  | p. 1 | 1 |

| 4.2 Timing correction                                     |      |   |

| 7.2 Thing Correction                                      | p. 1 | 1 |

| 5. Conclusion                                             | p. 1 | 1 |

### Introduction

When comparing test results taken on the bench with a high performance oscilloscope and data taken with a digital test system, quite often the questions arise like: Why does the data not match? Where are all the errors coming from?

This paper describes the phenomena associated with testing high speed devices on a high performance test system and provides a procedure to correlate measurement data.

# 1. Test System Error Terms

The systematic limits for measurement accuracy are given by the test system's AC and DC specifications.

Definition: Edge placement accuracy is the worst case deviation of actual value from programmed value.

Consider a typical propagation delay measurement where two timing edges are involved: One edge drives the "clock" input of the part, the other is strobing the output data of the part. Therefore, the placement error of the drive edge, the placement error of the strobe (compare) edge and the drive to receive offset (round trip error) contribute to the measurement error:

placement accuracy drive

- + placement accuracy strobe

- + drive to receive offset

- = measurement error

In case of a set up/hold time measurement which is related to two input edges, the systematic measurement error changes to:

placement accuracy of drive a + placement accuracy of drive b

Besides the edge placement error, the DC accuracy has to be taken into account which determines the worst case deviation of actual drive levels and compare thresholds from programmed values.

Note: This assumes that the DUT is "perfect", which means: does not interfere with the tester.

<sup>=</sup> measurement error

# 2. Error Terms due to Interfacing

The device under test (DUT) provides both the AC and the DC loads for the tester. Conversely, the tester output provides the load for the DUT

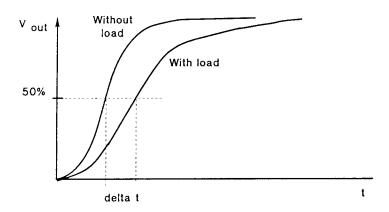

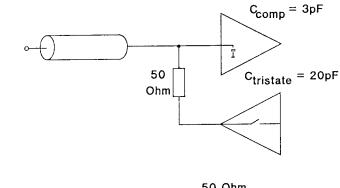

Figure 1. Capacitive loading of tester output

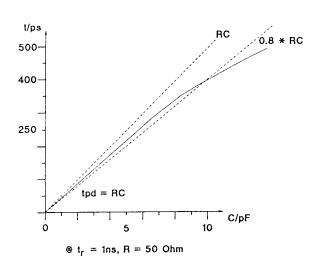

Figure 2. Timing error as function of RC time constant

# 2.1 AC Loading of Tester Output by DUT

The input capacitance of the DUT and the pin driver's output impedance, which is in general matched to the line impedance of the system, act as a low pass filter thus degrading the effective slewrate the higher the load is.

The resulting timing error (additional delay) is dependent on the intrinsic risetime of the source and the resulting RC time constant.

As a rule of thumb, the timing error at the 50% reference point is:

$$delta tpd = 0.8*Z_L* delta C$$

This equation is valid in case of small values of RC.

### Example:

$$Z_{L} = 50 \text{ Ohm}$$

# 2.2 DUT Input Threshold Versus Actual Tester Drive Levels

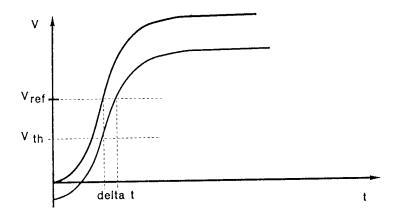

Test System timing calibration is referenced to the 50% point of the drive signal. In case the input threshold of the DUT differs from this point, a timing error comes into play which is given by:

## Example:

If you apply  $v_{ie} = OV$ ,  $v_{ih} = 5V$  to a TTL device, the Test System is referenced to 50% of this 5V swing:

$$v_{ref} = 2.5V$$

Actual TTL threshold is:

$$v_{th} = 1.4V$$

This leads to a timing error of:

$$delta t = \frac{\frac{\text{delta v}}{\text{slewrate}}}{\frac{2.5\text{v} - 1.4\text{v}}{2\text{v/ns}}}$$

= 550ps

The input circuit as well as additional loads may also bias the tester outputs thus changing the actual drive conditions.

Whereas the bias current (Ib) in most practical cases (CMOS, ECL) may be negligible because of the low source impedance, an ohmic load, e.g. a resistive divider scope probe (500 Ohms or 1000 Ohms), cannot. So a timing error is introduced which is directly proportional to the DC level change with respect to the DUT input threshold. (see figure 3.)

Figure 3. Timing error introduced by level change

# 2.3 DUT Output AC Loading by Tester

For highest accuracy at high speeds the terminated environment is mandatory (termination at receivers plus resitive divider). This technique reduces the capacitive loading to a minimum (about < 10pF) and provides an ohmic (DC) load instead.

(see App.Note "Testing High Speed Devices")

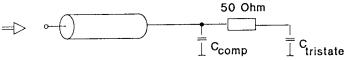

Figure 4. Timing error due to tristate capacitance

Figure 5. Timing error due to DC offset of comparator threshold

If instead operation into an open (High Z) environment is considered, besides the danger of reflections, the High Z (tristate) capacitance C<sub>trist</sub> of the pin electronics introduces a low pass filter adding a timing error.

The resulting timing error can be calculated analog to chapter 2.1 with

### 2.4 DC Threshold Considerations

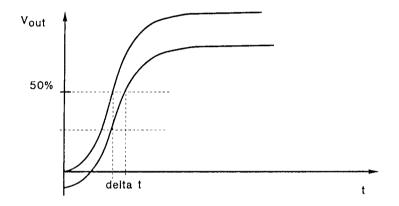

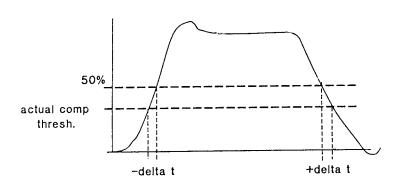

If tester comparator threshold reference differs from DUT timing reference, a timing error is introduced which is proportional to the voltage difference and the DUT output slewrate:

$$delta t = \frac{delta v}{slewrate (DUT)}$$

DC tolerances e.g. comparator threshold errors and termination voltage errors affect timing accuracy in the same way.

Note: A DC offset of the comparator threshold leads to different propagation delay readings for positive and negative going output edges! (see Fig. 6)

### 2.5 DUT Wiring

DUT wiring which differs from where the cal reference was taken have to be considered for subnanosecond accuracy. Any interconnect introduces a prop delay proportional to its length. On standard FR4 PCB's, the velocity of signals is about 15 cm/ns (0.5 foot/ns).

Figure 7. This trace is equivalent to 135ps!

# 2.6 DUT Specifics

Whereas the tester views all active vectors when it performs e.g. a prop delay test, a scope only sees a few vectors which might not be the device's worst case condition.

A scope needs repetitive patterns, the tester takes measurements in single shots. This can affect the thermal conditions (CMOS, GaAs), which in turn can change timing performance of the part.

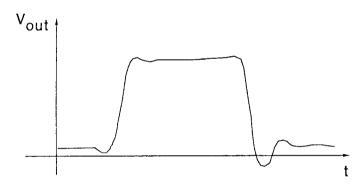

Parts typically tend to have different prop delays for rising and falling transitions because of different transition times and internal offsets.

Figure 8. Typical TTL output waveform

# 3. Correlation Procedure

From the summary of the various associated interfacing error terms and their values it becomes very obvious that they have to be ruled out carefully to get precise measurement results.

### 3.1 Calibration

The first step is to calibrate the equipment.

The HP82000 system offers three different calibration options:

1. Standard AC Cal

$$= > +/-500 \text{ ps (D200)}$$

:

With the standard AC calibration any parameter can be changed:

- data formats

- timing (LE,TE)

- period

- driver levels

- threshold

- pattern.

The error terms for this option are given by the environment temperature and humidity, crosstalk between the channels, jitter of the master clock, master clock accuracy, non-linearity of the delay circuit and by the ageing of the system.

2. Standard AC Cal at test period => +/- 350 ps (D200)

With the standard AC calibration at test period the following parameters might/must not be changed:

Parameter not to change:

- period

Parameters to change:

- data formats

- timing (LE, TE)

- driver levels (\*)

- thresholds

- pattern.

Fixing to one period setting eliminates the frequency dependency of the system.

3. User AC Cal = > +/- 250 ps (D200)

With the user calibration we can achieve the best accuracy. Parameters to change / not to change are:

Parameters <u>not</u> to change:

- period

- timing (LE, TE)

- data formats

- driver levels (\*)

Parameters to change:

- pattern

- thresholds.

Note: User calibration tunes the system for <u>one</u> specific timing setting, so in case of search functions those pins used for searching should <u>not</u> be included in user cal.

Make sure that your reference oscilloscope is calibrated (AC and DC), too.

# 3.2 Eliminate System Roundtrip Error Term

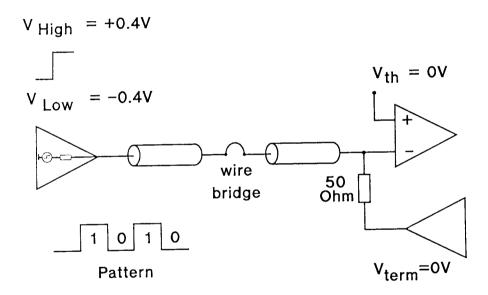

Replace your device under test (DUT) by a short piece of wire connecting your reference input (e.g. clock input) with the output under test. Set up the following simple test:

Read "prop delay" of this simple test and enter this reading in the PIN ATTRIBUTES file for SATR. Download this file to hardware and check the "prop delay" once again.

The SATR adds a virtual common delay between drive and receive path, thus compensating for the reading offset for a prop delay measurement.

# 3.3 Compensation for Capacitive Load

In case the input capacitance is well known, a compensation value for the loading effect can be calculated according to formula, delta tpd = 0.8 Z<sub>i</sub> delta C and added to the SATR entry.

In case the capacitance is not known, the risetime degradation of the drive signal due to the DUT input loading should be measured with the scope. The timing delta at the 50% reference level can then be entered in the SATR field.

Note: Take into consideration that the scope itself adds some capacitive loading. So for precise comparisons keep the probe always hooked up all the time (or compensate for the C of the probe tip).

# 3.4 Input Level Considerations

Verify that you reference your scope measurement to actual levels present at the inputs of the DUT under test to rule out any DC offsets or DC loading effects. Keep the probe hooked up to the test system to maintain loading conditions. Compensate for DC loading of probe by adjustment of drive levels.

# 3.5 Device Output DC Loading

In case of a terminated environment, the tester comparator "sees" a true image of the signal you can observe at the output of the DUT with the scope. So no additional correction is necessary.

In case of an unterminated environment, the signal will be distorted due to reflections from the open end. Besides that the additional tristate capacitance has to be taken into account.

# 3.6 Comparator Reference Adjustment

As discussed in chapter 2.4, any DC offset causes timing errors. In order to compensate for these, it is important to "calibrate" the scope view on what the tester "sees". A means of doing that is to perform a dynamic V<sub>oh</sub>/V<sub>ol</sub> test (output voltage sensitivity). Read out these values and center the comparator reference setting to 50% point of these values. Read the same values with the scope and set the scope level marker to 50% of scope reading. This method eliminates the DC offsets. Again it is necessary to keep the probe of the scope hooked up all the time so that the loading conditions for the DUT remain constant.

### 3.7 DUT Specifics

If your scope reading and the test results from the test system are not matching closely after this procedure, you should verify whether the differences are related to DUT specifics.

- 1. Thermal effects: Especially in CMOS applications, thermal effects may have to be considered. Hence the scope requires a repetitive trigger, you will run the part in a continuous loop to perform your scope measurements. In contrast to that, the test system performs its measurements in single shots. This can cause a temperature difference between both measurements affecting the timing performance. Heat up or cool down the part and observe the behavior of the part on the scope. An "extension" of the single shot measurement by adding a long dummy init loop with the sequencer can also help to approach similar test conditions.

- 2. The scope "sees" only a small portion of your vector range: To eliminate any effects due to transitions which are not in your view, mask out all other transitions by use of the word mask/pin mask.

An alternate method to eliminate timing offsets is to use one DUT which has been thoroughly evaluated, e.g. on the bench with a scope, and adjust the test system to it. Now, this part becomes your "calibration" reference or your "golden" device.

### 4.1 Threshold Adjustment

Go through the same procedure as per chapter 3.6 to eliminate the threshold offset of the comparators and any loading effect.

# 4.2 Timing Correction

Run the prop delay test function and read the value, compare it to your scope reading and enter the difference in the SATR. Repeat the test and verify that your reading difference is now close to zero. By following carefully through this procedure you can quantify and rule out your interfacing errors and reduce your systematic measurement error terms.

Typically you can achieve good correlation down to 150 to 200ps.

#### U.K.

Hewlett-Packard Ltd. Customer Information Centre King Street Lane Winnersh GB-Wokingham Berkshire RG11 5AR (734) 777828

### Germany

Hewlett-Packard GmbH Vertriebszentrale Deutschland Hewlett-Packard-Straße D-6380 Bad Homburg (6172) 16-0

#### France

Hewlett-Packard France Parc d'activité du Bois-Briard 2, av. du Lac F-91040 Evry Cedex (1) 69861725

#### Italy

Hewlett-Packard Italiana S.p. A. Via G. di Vittorio 9 I-20063 Cernusco S/N (MI) (02) 923691

### For all other European Countries:

Hewlett-Packard Central Mailing Department P.O. Box 529 NL-1180 AM Amstelveen The Netherlands (31) 205479999

### **United States:**

Hewlett-Packard Company 4 Choke Cherry Road Rockville, MD 20850 (301) 670-4300

Hewlett-Packard Company 5201 Tollview Drive Rolling Meadows, IL 60008 (312) 255-9800

Hewlett-Packard Company 5161 Lankershim Blvd. No. Hollywood, CA 91601 (818) 505-5600

Hewlett-Packard Company 2015 South Park Place Atlanta, GA 30339 (404) 955-1500

#### Canada:

Hewlett-Packard Ltd. 6877 Goreway Drive Mississauga, Ontario L4V1M8 (416) 678-9430

## Australia/New Zealand:

Hewlett-Packard Australia Ltd. 31–41 Joseph Street Blackburn, Victoria 3130 Melbourne, Australia (03) 895-2895

### Africa/Middle East:

Hewlett-Packard Central Mailing Department P.O. Box 529 NL-1180 AM Amstelveen The Netherlands (31) 205479999

### Far East:

Hewlett-Packard Asia Ltd. 22 F Bond Centre West Tower 89 Queensway Central, Hong Kong (5) 8487777

#### Japan:

Yokogawa-Hewlett-Packard Ltd. 29 – 21, Takaido-Higashi 3-chome Suginami-ku, Tokyo 168 (03) 331-6111

### Latin America:

Hewlett-Packard Latin America Region Headquarters Monte Pelvoux Nbr. 111 Lomas de Chapultapec 11000 Mexico, D.F. Mexico (905) 596-79-33

Copyright © 1990 Hewlett-Packard GmbH Printed in the Federal Republic of Germany 9/90 5952-2311